El diseño del sistema de control de este proceso se puede implementar utilizando máquinas de estado, empleando para este caso en particular el modelo Mealy, por cuanto las salidas dependen tanto de las señales de entradas como del estado actual para cambiar de ciclo.

Por su parte, para la implementación del diseño se plantea utilizar una FPGA de Xilinx, por presentar estos dispositivos las características y prestancias requeridas. Cabe resaltar, que la ejecución concurrente del algoritmo implementado en la FPGA, permite además obtener una elevada velocidad de ejecución que difícilmente se puede conseguir con otros dispositivos digitales de carácter genérico.

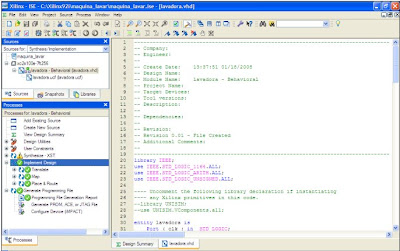

Así mismo, el diseño y la respectiva programación de la FPGA, se realizó mediante dos formas: implementando el circuito digital y empleando un lenguaje de descripción de hardware como VHDL. Para ello, se utilizó el software ISE 9.2i de Xilinx, el cual permite llevar a cabo la programación de FPGAs y CPLDs por los dos métodos mencionados anteriormente.

El dispositivo FPGA empleado para realizar la simulación es XC2S100E-7FT256, seleccionado por ser de bajo costo y posser la cantidad de compuertas necesarias para la implementación del diseño propuesto en esta investigación.

Finalmente, se presentan las simulaciones del sistema de control, donde se evidencia el correcto funcionamiento del mismo con sus respectivas entradas, salidas y ciclos del proceso.

El proceso de lavado, en máquinas de lavar automáticas domésticas, se lleva a cabo mediante una serie de ciclos en función de las variables de entrada y de la secuencia de los ciclos de trabajo. Básicamente las entradas y salidas del sistema de control y los ciclos de operación son los siguientes:

1.1.- Señales de entrada:

- Start: Cuando está en alto se inicia el proceso, una vez iniciado el proceso esta señal no tiene efecto.

- Vacío: Cuando está en alto indica que el tambor de agua se encuentra vacío.

- Lleno: Cuando está en alto indica que el tambor de agua se encuentra lleno.

- Clk: Reloj del sistema de control.

- Llenar: Cuando está en alto abre las válvulas para llenar el tambor de agua.

- Vaciar: Cuando está en alto abre las válvulas para vaciar el tambor de agua.

- Lento: Cuando está en alto hace girar el motor con la dirección indicada por la señal Dirección, con un ritmo lento. Esta velocidad se usa en los ciclos de lavado y de enjuagar.

- Rápido: Cuando está en alto hace girar el motor con la dirección indicada por la señal Dirección, con un ritmo rápido. Esta velocidad se usa sólo en el ciclo de exprimir.

- Dirección: Indica la dirección en la cual se moverá el tambor, en alto gira hacia la izquierda y en bajo hacia la derecha. El tambor debe moverse alternativamente de derecha a izquierda en los ciclos de lavado y de enjuagar, y girar en la misma dirección en el ciclo de exprimir.

- Inicial: Es el estado inicial de la máquina y espera que se levante la señal Start para que se inicie el proceso de lavado.

- Lavado: En este ciclo se llena de agua el tambor y se hace girar alternativamente el motor de derecha a izquierda durante 20 minutos con una velocidad lenta, y luego se vacía el tambor de agua.

- Enjuagar: Se llena el tambor de agua nuevamente y se hace girar alternativamente el motor de derecha a izquierda durante 5 minutos con una velocidad lenta, y luego se vacía el tambor de agua.

- Exprimir: Este ciclo hace girar el motor en un sólo sentido durante 5 minutos con una velocidad rápida, para finalmente vaciar el tambor de agua y volver al estado Inicial.

Figura 1. Diagrama de entradas y salidas para una lavadora automática doméstica.

2. DISEÑO DEL SISTEMA DE CONTROL MEDIANTE FPGA

Para el diseño del sistema de control digital se empleó el modelo de Mealy de máquinas de estado, lo que permite definir todo el proceso de lavado en ciclos, con funciones específicas dependiendo de las entradas y del estado actual del sistema. En la Figura 2 se presenta la secuencia de estados del proceso de lavado.

Figura 2. Secuencia de estados del proceso de lavado.

En la actualidad se cuenta con la ayuda de entornos de desarrollo especializados en el diseño de sistemas digitales con FPGA para diversas aplicaciones. Un diseño en FPGA se puede llevar a cabo, ya sea como un diagrama esquemático, o haciendo uso de un lenguaje de descripción de hardware (HDL), en pro de las facilidades del diseñador.

Como consecuencia de ello, para implementar el diseño del sistema de control se propone emplear una FPGA de Xilinx en función de sus excelentes características y altas prestancias, sumado a ello, el fabricante proporciona de manera gratuita el software ISE 9.2i, lo que permite realizar el diseño de una forma rápida y sencilla.

A continuación se presentan los diseños para el sistema de control usado en lavadoras automáticas mediante diagrama esquemático y con HDL.

2.1 DISEÑO DEL SISTEMA DE CONTROL BASADO EN DIAGRAMA ESQUEMÁTICO

El diseño del sistema está basado en una máquina de estados tipo Mealy, por ello en primera instancia deben determinarse las ecuaciones combinacionales y secuenciales que satisfacen el proceso. En tal sentido, se realiza una tabla de verdad a fin de especificar el estado futuro del sistema, así como los valores de entrada que deben tener los Flip Flop empleados. Por simplicidad, se han utilizado los Flip Flop tipo D, y debido a que el proceso está compuesto por 6 seis estados (inicio, lavado, vacío1, enjuague, vacío2 y exprimido), se requieren sólo 3 de ellos.

La tabla de verdad realizada consta de 7 variables de entrada, lo cual implica 128 posibles combinaciones  y por esta razón no se presenta en este artículo. Sin embargo, como resultado de ella, las ecuaciones de la lógica digital que deben estar presentes en cada una de las entradas de los Flip Flop son las siguientes:

y por esta razón no se presenta en este artículo. Sin embargo, como resultado de ella, las ecuaciones de la lógica digital que deben estar presentes en cada una de las entradas de los Flip Flop son las siguientes: (1)

(1)

(3)

(3)Donde:

T: Señal que indica que se ha cumplido el tiempo de lavado, enjuague o exprimido.

S: Señal de inicio del proceso.

V: Señal que indica que el tambor de agua de la lavadora esta vacío.

L: Señal que indica que el tambor de agua de la lavadora esta lleno.

La señal T es obtenida mediante la comparación del valor de un contador con ciertos valores prefijados para realizar la temporización de 5 y 20 minutos requerida en los ciclos de lavado, enjuague y exprimido. La ecuación respectiva a la variable T está relacionada con algunos parámetros que se definirán a continuación:

Dato1: Corresponde al valor digital precargado en un comparador para satisfacer los 5 minutos requeridos en los ciclos de enjuague y exprimido.

Dato2: Corresponde al valor digital precargado en un comparador para satisfacer los 20 minutos requeridos en el ciclo de lavado.

Contador: Es un contador que se incrementa con cada flanco de subida de la señal de reloj.

Finalmente, la ecuación correspondiente a la variable T es la que se muestra a continuación:

(4)

(4)Puesto que la señal Contador es común a ambos comparadores, y que éstos no poseen entradas de habilitación/deshabilitación, es necesario incorporar el término que involucra el estado actual del sistema (Q0, Q1 y Q2) a la salida del primer comparador a fin de restringir su uso sólo a los ciclos de enjuague y exprimido.

Por su parte, el Contador sí posee entrada de habilitación, además dispone de una entrada para realizar reset asíncrono. Las ecuaciones de la lógica conectadas a dichas entradas son las siguientes:

(5)

(5) (6)

(6)La señal definida como Enable_cont posee un nivel lógico alto en los estados lavado, enjuague y exprimido y la señal CLR_cont posee el nivel lógico alto en todos los demás estados a fin de garantizar que el contador se encuentre en cero cuando se establezca la señal de habilitación.

Para determinar las expresiones correspondientes a cada una de las salidas, se realiza una nueva tabla de verdad, la cual se muestra en la tabla 1.

Tabla 1: Tabla de verdad para determinar el circuito lógico combinacional requerido en cada salida del sistema.

(7)

(7) (9)

(9) (10)

(10) (11)

(11)Donde:

CLK: Es la señal de reloj del sistema.

La señal de Dirección no se encuentra contenida en la tabla 1, sin embargo, su ecuación ha sido obtenida por una simple inspección de la función que debe realizar en el proceso. Esta debe variar entre 0 y 1 cuando se habilita la señal Lento, además, debe establecerse en 0 (giro en sentido horario) cuando se habilite la velocidad Rápido, es decir, cuando se alcance el estado para exprimir.

Figura 3. Diagrama esquemático del diseño.

Los lenguajes de descripción de hardware facilitan la descripción de circuitos digitales complejos, con la finalidad de facilitar el trabajo al diseñador. Entre los principales lenguajes tenemos VHDL, Verilog y ABEL.

Por su parte, para la descripción del hardware del sistema digital propuesto se empleó VHDL, por ser éste un lenguaje textual de alto nivel que proporciona ciertas ventajas con respecto a los mencionados anteriormente, tales como: es un lenguaje estándar, ofrece flexibilidad de implementación, el código es portable entre herramientas, entre otras.

En el algoritmo diseñado en VHDL, para el sistema de control digital, se colocaron todas las salidas en el mismo proceso donde se colocó la transición de estados, esto implica que la salida cambiará un ciclo de reloj después que cambie el estado, pero este hecho no afecta el buen funcionamiento del sistema por cuanto la frecuencia de reloj es suficiente para que este efecto no sea percibido por el usuario. Particularmente, las salidas se han colocado en la propia descripción de la máquina, lo cual implica que vienen sincronizadas por la señal de reloj.

A continuación se presenta el algoritmo desarrollado en VHDL para el sistema de control empleado en lavadoras automáticas domésticas:

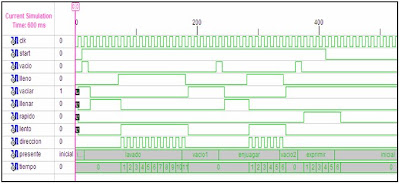

Una vez finalizado el diseño del circuito digital se realizó la simulación para verificar su funcionamiento y los resultados se muestran en la figura 4. En esta figura, las señales denotadas como S, V y L son las entradas y corresponden con las señales Start, Vacío y Lleno, respectivamente. Las señales presentadas como Q0, Q1 y Q2 permiten verificar la secuencia de las demás señales en función del estado en que se encuentran. Por otra parte, Min5 y Min20 corresponden a las salidas de los comparadores para obtener las temporizaciones de 5 y 20 minutos respectivamente y T es la señal indicadora de finalización del tiempo requerido. Es importante destacar que para el desarrollo de la simulación se empleó una señal de reloj de 100 Hz y para facilitar visualización y análisis, el tiempo correspondiente a 20 minutos fue sustituido por sólo 10 ciclos de reloj y el de 5 minutos por 5 ciclos.

Figura 4. Diagrama de tiempo del proceso obtenido con el diseño esquemático.

Figura 5. Diagrama de tiempo del proceso obtenido con el diseño en VHDL.

Además, en la figura 5 se observa una señal denominada tiempo, la cual es el contador de los ciclos de reloj del sistema, y tiene como función proveer las temporizaciones de 5 y 20 minutos correspondientes a los ciclos de lavado, enjuague y exprimido.

Finalmente en las figuras 6 y 7, se presenta la distribución de los pines usados en el dispositivo y, el reporte de las características del diseño, respectivamente. Así mismo, el reporte contine la cantidad de recursos empleados (puertos de I/O, LUTs, latches, etc) y los que se encuentran disponibles. En las figuras 8 y 9 se presentan los resultados correspondientes al proceso de síntesis del diseño realizado en diagrama esquemático y en VHDL, respectivamente.

Para configurar la FPGA es necesario crear el fichero con extensión .bit y ejecutarlo posteriormente con el programa iMPACT.

Figura 6. Distribución de los pines de I/O en la FPGA.

Figura 6. Distribución de los pines de I/O en la FPGA.

Figura 7. Resumen de las características del diseño.

Figura 8. Resultado del proceso de síntesis del diseño realizado en diagrama esquemático.

Figura 9. Resultado del proceso de síntesis del diseño realizado en VHDL.

4. CONCLUSIONES

Descargar paper, hacer click en:

http://docs.google.com/Doc?docid=dgf2h5rb_0dmb6mmc4&hl=en

- Ing. Noelia Tarazona

- Ing. Reinaldo Peraza